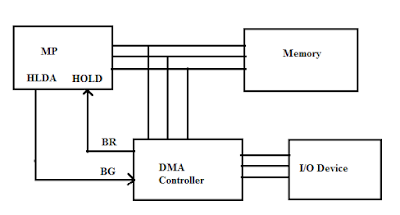

- DMA is a process of communication for data transfer between memory and input/output, controlled by an external circuit called DMA controller, without involvement of CPU.

- 8085 MP has two pins HOLD and HLDA which are used for DMA operation.

- First, DMA controller sends a request by making Bus Request (BR) control line high. When MP receives high signal to HOLD pin, it first completes the execution of current machine cycle, it takes few clocks and sends HLDA signal to the DMA controller.

- After receiving HLDA through Bus Grant (BG) pin of DMA controller, the DMA controller takes control over system bus and transfers data directly between memory and I/O without involvement of CPU. During DMA operation, the processor is free to perform next job which does not need system bus.

- At the end of data transfer, the DMA controller terminates the request by sending low signal to HOLD pin and MP regains control of system bus by making HLDA low.

|

| Direct Memory Access (DMA) |

|

| Fig: DMA Controller |

- Figure shows the block diagram of a typical DMA controller. The unit communicates with the MP via the data bus and control lines.

- The registers in the DMA are selected by the MP through the address bus by enabling the DS (DMA select) and RS (Register Select) inputs. The RD (read) and WR (write) inputs are bidirectional.

- When the bus grant (BG) input is 0, the MP can communicate with the DMA registers through the data bus to read from or write to the DMA registers. When BG=1, the processor does not have control over the system buses and the DMA can communicate directly with the memory by specifying an address in the address bus and activating the RD or WR control.

- The DMA controller has three registers: an address register, a word count register and a control register.

- The address register contains an address to specify the desired location in memory. The address bits go though bus buffers into the address bus. The address register is incremented after each word that is transferred to memory.

- The word count register holds the number of words to be transferred. The register is decremented by one after each word transfer and internally tested for zero.

- The control register specifies the mode of transfer.

#8237

Good Job

ReplyDeleteShort and precise. Nice

ReplyDeleteVery nice 👌

ReplyDeleteNice explanation

ReplyDeleteI did understand in class but this one is interesting 🤗

ReplyDeletethank you, to the point explanation

ReplyDeleteHelpful

ReplyDeletenice!!!!

ReplyDeleteLOVED THE DIAGRAMS

ReplyDelete